메모리 계층구조

| 메모리 계층구조 | 메모리 시스템은 바이트들의 선형배열이다. CPU 레지스터들은 가장 자주 이용하는 데이터를 보관한다. 작고 빠른 캐시 메모리는 비교적 느린 메인 메모리에 저장되어있는 데이터와 인스트럭션을 미리 올려놓아, 상위 메모리에서 보다 빠르게 접근할 수 있게 구성되어있다. 메모리 계층의 바닥으로 갈 수록 저렴하고 많은 용량을 저장할 수 있어, 단계적으로 캐시 메모리를 두어 보다 빠르게 데이터에 접근할 수 있게 구성되어있다. |

저장장치 기술

| RAM | Random access memory는 정적램(SRAM), 동적램(DRAM)으로 나뉜다. 정적램은 동적램보다 훨씬 더 빠르고 훨씬 더 비싸다. SRAM은 캐시 메모리로 사용되며 CPU 칩 내부 또는 외부에 장착된다 (L1, L2, L3) DRAM은 메인 메모리와 그래픽 시스템의 프레임 버퍼로도 사용된다. |

| 정적 RAM | SRAM은 트렌지스터로 구성되어있으며 이중안정 본성으로 인해 전원이 공급되는 한 자신의 값을 무한히 유지하게 된다. - DRAM에 비해 안정적이다. |

| 동적 RAM | DRAM은 각 비트를 캐패시터에 저장한다. 이 캐패시터는 엄청 작어서 집적도를 매우 높일 수 있다. DRAM은 SRAM과 달리 외란에 대해서 매우 민감해 캐패시터 전압이 달라지면 다시 회복할 수 없다. |

| 일반 DRAM | DRAM은 rows와 columns로 이루어진 직사각형의 배열로 구성되어있다. 여기서 데이터를 가져오는 방법은 먼저 row에 해당하는 요청을 보내는데 이를 RAS(row access strobe) 요청이라고 부른다. 이렇게 요청받은 row를 buffer에 넣어놓고, 다음 column 정보인 CAS(column access strobe) 요청에 해당하는 8bit 값을 복사해서 메모리 컨트롤러로 보낸다. |

| 이차원 배열구조 | 이러한 이차원 배열구조의 단점은 주소가 두 단계로 보내져야 하며, 이로 인한 접근시간이 증가한다는 점이다. |

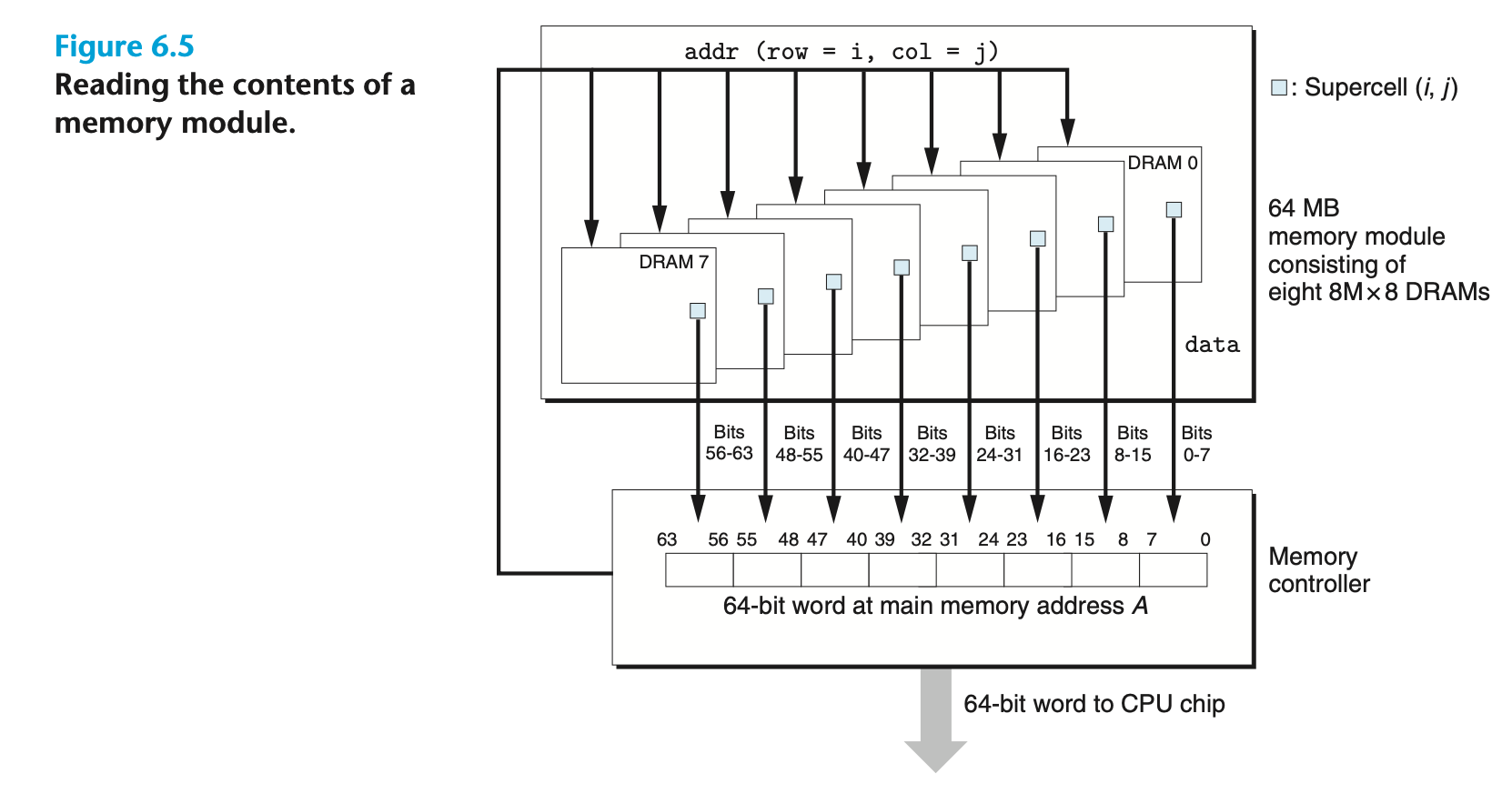

| 메모리 모듈 | 한번의 요청에 보다 많은 데이터를 전송하기 위해 다음과 같은 방법을 사용한다. 각 슈퍼셀들은 1바이트의 메인 메모리를 저장. 묘듈내의 회로는 이 출력들을 모아 64비트 워드로 구성하고 이를 메모리 컨트롤러에 돌려준다. |

| 지역성 | 잘 작성한 컴퓨터 프로그램은 좋은 지역성을 보여준다. 지역성은 일반적으로 두 개의 서로 다른 형태를 가지는것으로 설명된다. (시간 지역성과 공간 지역성) 한번 참조된 메모리 위치는 가까운 미래에 다시 여러번 참조될 가능성이 높고, 마찬가지로 근처의 메모리 위치를 참조할 가능성이 높다. |

메모리 계층구조 - 캐시

| 캐시 | 레벨 K에 있는 캐시는 레벨 K+1에서 온 블록들의 부분집합의 사본을 저장하고 있다. |

| 캐시 적중 | 현재 레벨 K에 저장된 블록들 중의 하나에서 d를 찾는다. 만약 d가 K에서 우연히 캐시되어 있다면, 이 경우를 캐시 적중이라고 한다. |

| 캐시 미스 | 만일 데이터 객체 d가 레벨 K에서 캐시되지 않는다면 캐시미스가 발생한 것이다. 만약 레벨 K 캐시가 이미 꽉 찬 상태라면 기존 블록에 덮어쓰기도 한다. 여기서 축출되는 블록은 희생블록이라고 부른다. 어떤 블록을 교체할지에 관한 결정은 캐시의 교체 정책에 의해 정해진다. |

캐시 메모리

| 기본 캐시 메모리 구조 | 해당 시스템에 대한 캐시는 S = 2^s개의 캐시 집합의 배열로 구성된다. 하나의 배열에는 E개의 캐시 라인들로 이루어져 있으며 각 라인은 B = 2^b 바이트의 데이터 블록, 유효비트, 태그비트(key값이라고 생각하면 될듯)로 구성된다. 캐시의 크기 C는 S * E * B로 나타낸다. 여기서 유효비트와 태그비트는 포함되지 않는다. 캐시는 요청된 워드를 간단히 주소비트만 조사해서 찾아낼 수 있도록 구성되어 있으며 한순한 해시 함수를 하용하는 해시 테이블과 유사하다. |

| 직접 매핑 캐시 | 집합당 정확히 한개의 라인을 갖는 경우로 주로 캐시미스가 발생해도 빠르게 다시 하위 메모리에 접근할 수 있는 SRAM에서 주로 사용한다. |

| 직접매핑 캐시의 작업 | 집합 선택 캐시는 S개의 집합 인덱스 비트를 w의 주소 중에서 뽑아낸다. s bit 라인 매칭 해당 인덱스의 비트가 유효하고, tag비트와 일치하는지 확인한다. 워드 선택 오프셋 비트를 확인해 선택된 라인의 몇번째 블록을 가져올지 선택한다. |

| 집합 결합성 캐시 | 이 캐시의 경우에는 하나의 집합에 여러개의 라인을 가지고 있다. |

| 라인매칭과 워드 선택 | 여러개의 라인의 태그와 유효비트를 조사해야 하기 때문에 좀 더 복잡하다. 결합성 메모리는 각 집합의 키, 태그와 유효비트가 모두 결합되어 있다. |

| 완전 결합성 캐시 | 그냥 가상메모리의 TLB를 생각하면 편한데, 여기서 해당 캐시의 tag bits와 block을 합치면 하위 메모리의 주소가 된다. |

'Krafton_Jungle > Study' 카테고리의 다른 글

| Krafton_jungle 5기 7주차 WIL - OSI 7계층 (2) | 2024.05.02 |

|---|---|

| Krafton_jungle 5기 6주차 WIL - Exceptional Control Flow (0) | 2024.05.01 |

| Krafton_jungle 5기 6주차 WIL - Implicit free list (0) | 2024.04.27 |

| Krafton_jungle 5기 5주차 WIL - Exceptional Control Flow (0) | 2024.04.23 |

| Krafton_jungle 5기 5주차 WIL - Linker (0) | 2024.04.23 |